The N25Q is a high-performance multi-input/output serial flash memory device manufactured using 65nm NOR technology. It features in-place execution (XIP) capabilities, advanced write protection mechanisms, and a high-speed spi compatible bus interface. Innovative, high-performance, double and quadruple input/output instructions that double or quadruple the transmission bandwidth for READ and PROGRAM operations.

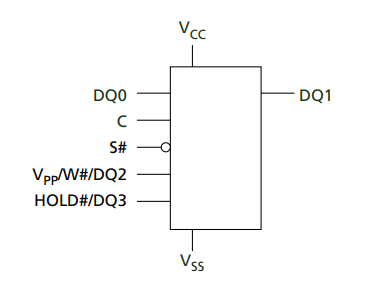

N25Q Logic Diagram

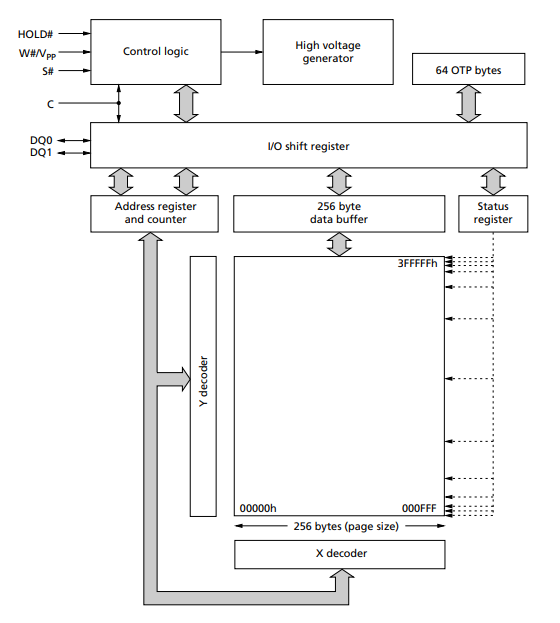

Block Diagram

Device Configurability

The N25Q series provides additional functionality to configure default and/or non-volatile Settings via the non-volatile configuration register. The Volatile setting can be configured using the Volatile and Volatile enhancement configuration registers. These configurable features include:

• Number of virtual cycles of the fast READ command

• Output buffer impedance

• SPI protocol type (extended SPI, double SPI, or quadruple SPI)

• Requires XIP mode

• Enable/disable HOLD (RESET function)

• Enable/disable line feed mode

Features

Memory is organized into 64 (64KB) primary sectors, each of which is further divided into 16 sub-sectors (for a total of 1024 sub-sectors).

Memory can erase a 4KB subsector at a time, 64KB sectors at a time, or entire sectors. According to application requirements, software can write protect memory through volatile and non-volatile protection features. The volatile protection granularity is 64KB(sector granularity).

The device has 64 OTP(one-time programmable) bytes, which can be read and programmed by the read OTP and PROGRAM OTP commands.

The 64 bytes can also be permanently locked with the PROGRAM OTP command. The device also has the ability to pause and resume PROGRAM and ERASE cycles by using dedicated PROGRAM/ERASE SUSPEND and resume instructions.

Operating protocol

The memory can be operated with three different protocols:

• Extended SPI (standard SPI protocol upgraded with dual and quad operations)

• Dual I/O SPI

• Quad I/O SPI

The standard SPI protocol has been extended and enhanced with dual and quadruple operations. In addition, the dual SPI and quad SPI protocols improve data access time and throughput for a single I/O device by transferring commands, addresses, and data over two or four data lines